昨天介紹了如何用Quartus建立一個project,在這個project裡可以建立許多不同類型的檔案。

今天要先來介紹如何建檔畫邏輯圖,如果有接上板子的話,可以用電路圖的方式操控FPGA~

(ps.第一篇寫畫電路圖,我沒搞清楚電路圖跟邏輯圖的差異,應該是邏輯圖,寫錯了很抱歉!)

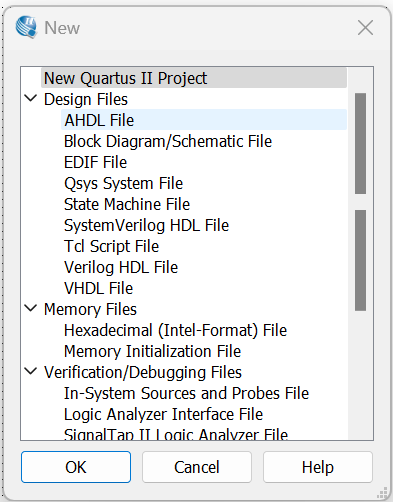

沿用昨天建立好的project,先在左上角的「File」選取「New」,接著會出現一個列表。

這裡可以選取要建立的檔案種類,今天要來畫邏輯圖,所以選取Design Files的「Block Diagram/Schematic File」。

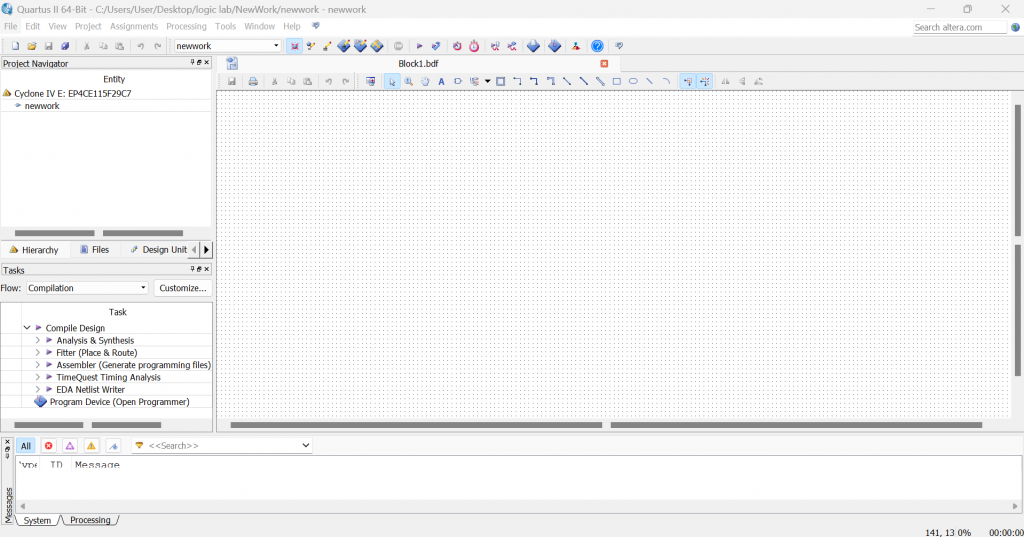

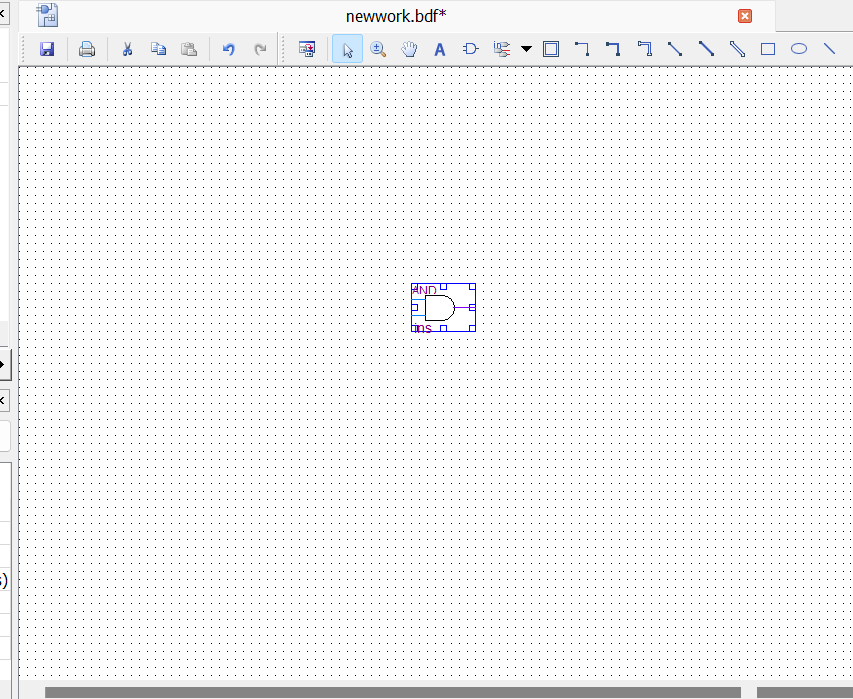

建立好後會看到畫面有很多的點:

接著要來處理這個檔案的名稱,如果沒有先做處理,之後執行時會出問題。

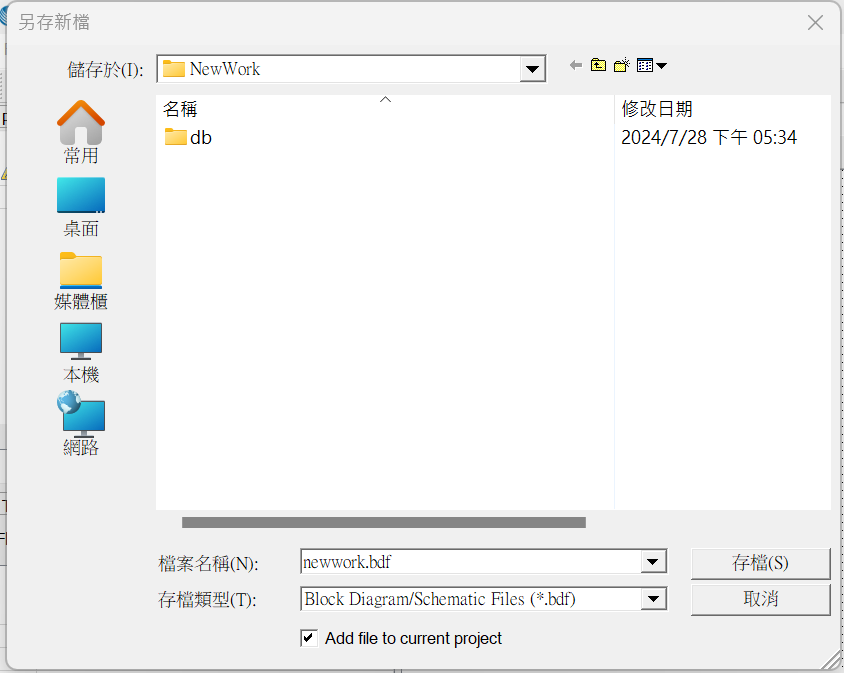

一樣到左上角的File,選取「Save as…」,接著會跳出一個小視窗,底下的檔案名稱會跟昨天取的project名稱一樣,如果檔案名稱沒有顯示的話就要自己打上,名稱得與project名稱一樣,否則也會出錯。名稱設定好後按存檔。

接著就到了加入邏輯圖元件的部分啦~

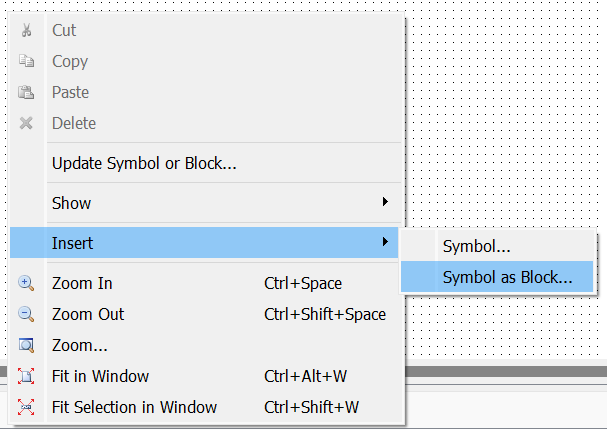

一開始的畫面什麼東西都沒有,首先先在畫圖的地方按右鍵,選取Insert,然後選Symbol as Block。

Libraries會有幾個資料夾可以選。

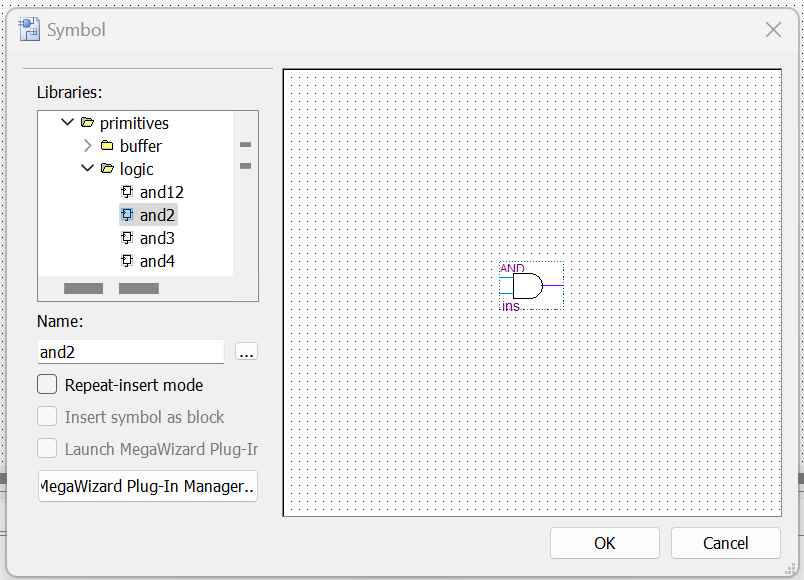

先來尋找最常見的AND gate、OR gate及INPUT、OUTPUT,他們都在primitives這個地方。

打開primitives後,會再看到幾個資料夾名稱,這些名稱都是元件的分類。

AND、OR都屬於邏輯的部分,所以選取logic,會看到底下出現邏輯元件。

以底下的圖來看,前面會寫元件邏輯名稱,後面的數字代表了他可接收幾個input。

選取好要使用的logic gate後,點OK,他就會出現在畫面中囉~

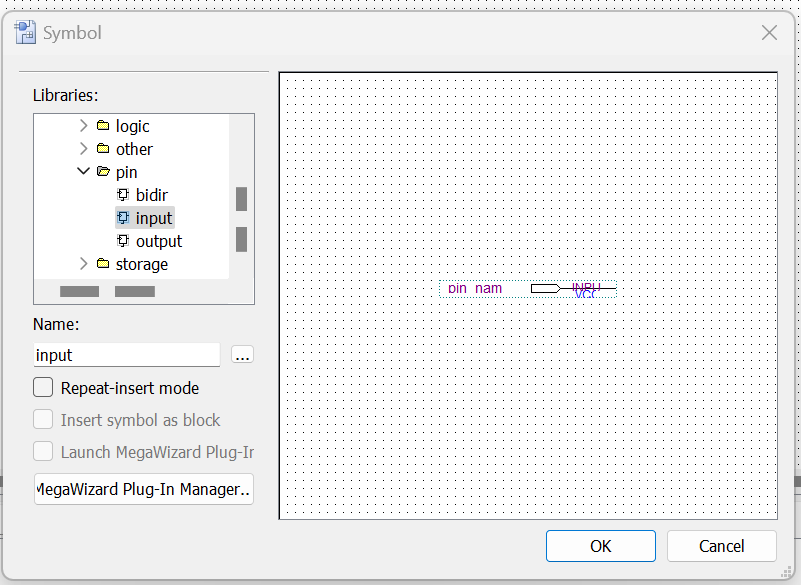

接著是INPUT及OUTPUT的部分,他們屬於pin這個類別。

一樣選取好後按OK,就會出現在邏輯圖中了!

然後跟寫程式時要幫變數取名稱一樣,幫元件取適當的名稱會比較好喔~

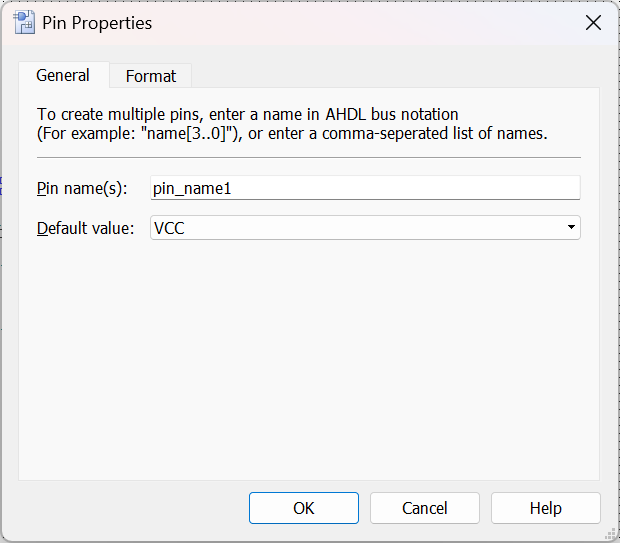

快速點擊兩下元件,就會出現以下的小視窗,可以在Pin name(s)來更改元件的名稱。

Default value的部分可以不用更動。

把所需要的元件都加入後,接著需要做接線的動作。

這裡還有許多其他的元件,可以根據需求來使用~這邊就先只介紹最基礎的元件。

接線的話,只要在元件的線端點,用滑鼠點擊拉出就可以了。

其中要注意的是,連接各個元件時,要注意有沒有「點」的出現。

這裡我想以例子做說明。

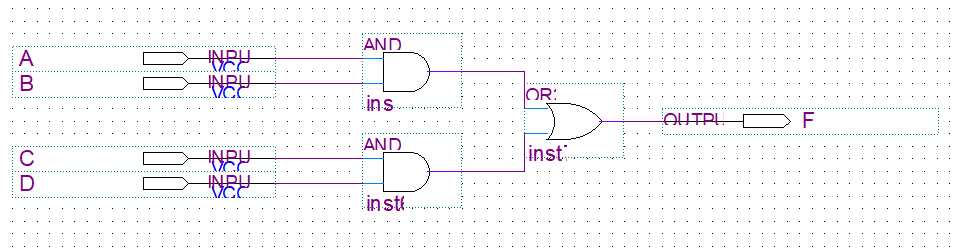

假如我今天要設計一個邏輯圖,要求是:F(A,B,C,D) = AB+CD

則邏輯圖會是這樣:

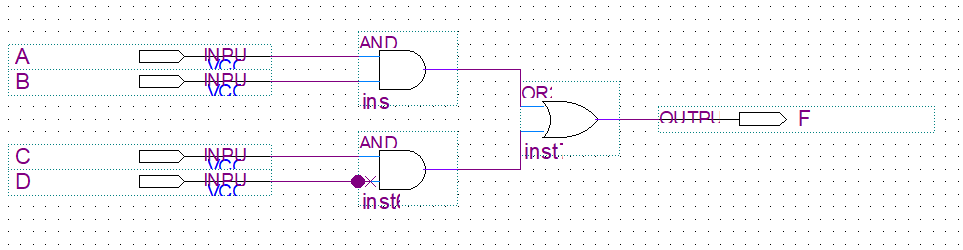

至於剛剛說到的不能出現「點」,指的是如果線沒有拉「剛好」,也就是沒有對準端點,就會出現「點」:

在D input 接到AND gate的地方,與上一張圖的差別就是在與AND連接的地方多出了一個「點」,這是因為在接線的時候,線會根據游標拉至哪裡,就接到哪裡,點的右邊有一個「X」,這個「X」是我游標放開的地方,也就是D input的線接到的地方。

雖然D input有確實接到AND gate,但因為接線位子並沒有準確的接至AND gate的input端點,所以產生了「點」,這樣的話會執行錯誤。

這個「點」代表不同的線相遇、交會的位子。

在連接gate時,要注意不能有「點」的出現。如果出現,就要重接。

畫好邏輯圖後,就可以儲存檔案、compile來看有沒有錯誤啦~

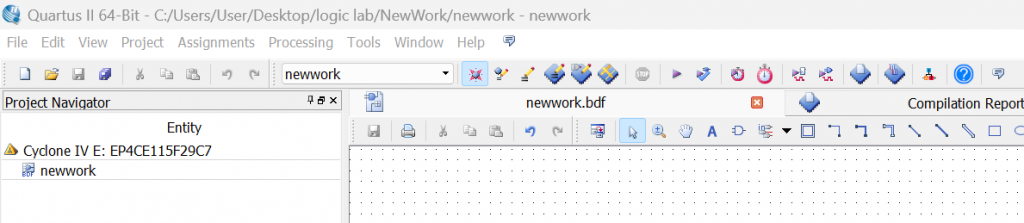

存好檔案後,按compile:

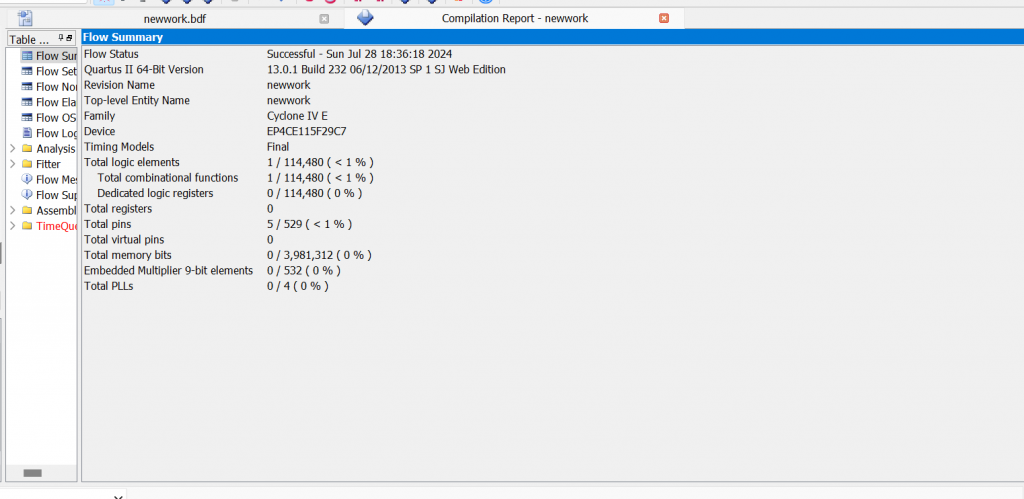

編譯的過程會有點久,在原先檔案的地方會出現Compilation Report:

編譯好後會出現以下的視窗:

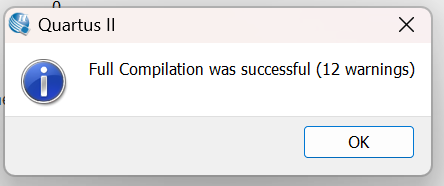

成功的話就會顯示Full Compilation was successful,後面可能會顯示warnings,如下圖,可以不用理他。

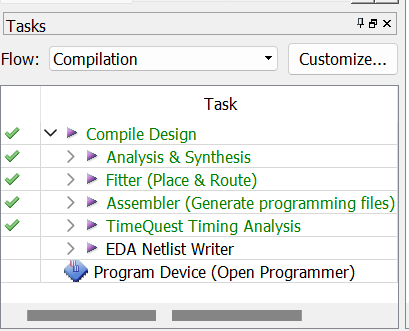

左邊會顯示編譯後每個Task的狀態:

都有打勾就代表都沒有問題!

如果編譯後有error,可以查看底下的Message,其中一個選項是「Show Error Messages」,圖示是一個紅色圓圈底的白色叉叉,很容易認出~這裡會顯示錯誤的原因,把這些錯誤修改就可以了~

今天的部分就這樣~個人認為最需要注意的地方就是接線時要注意不能出現點點,當時自己在這部分練習了很久XD